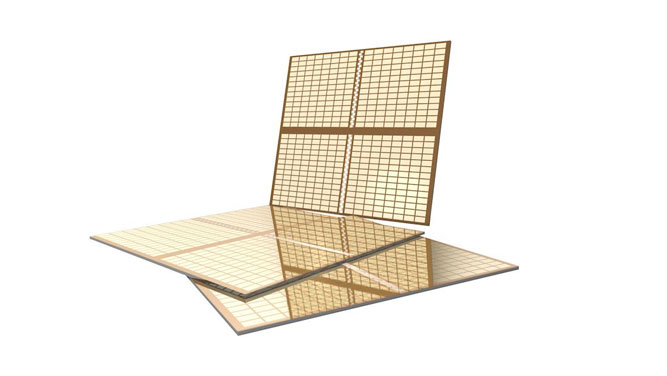

با اینکه هنوز تدوین استاندارد حافظه DDR5 از سوی JEDEC به پایان نرسیده، سازندگانی چون Cadence و Micron یک نمونه 16 گیگابیتی را توسعه دادهاند که می گویند تا پیش از پایان سال 2019 آماده تولید انبوه خواهد بود.

انتظار میرود JEDEC، گروهی که پشت استاندارد DDR برای حافظههای رم قرار دارد، همین امسال DDR5 را تدوین کند. با این حال به نظر میرسد Cadence و Micron بی تابی میکنند و میخواهند همین حالا با استاندارد در دسترس آماده باشند. CadenceاIP رابط(کنترلر و PHY)اDDR5 را توسعه داده و Micron اولین نمونه از قطعه سیلیکونی حافظه رم DDR5 را آماده کرده است. این دو در ماه مِی نمونه اولیهای با نرخ تبادل 4400MT/s (میلیون تبادل در ثانیه ) به نمایش گذاشتند.

به گفته یکی از مدیران Micron، تولید انبوه تراشههای 16 گیگابیتی DDR5 از اواخر سال 2019 میلادی با بهکارگیری یک فناوری ساخت کوچکتر از 18 نانومتری آغاز خواهد شد و سیستمهای مجهز به حافظه رم DDR5 در سال 2020 روانه بازار میشوند. مشخص نیست اینتل چه وقت پشتیبانی از این نسل جدید از تراشههای حافظه رم را به پردازندههای خود میآورد اما در آن سو AMD وعده داده تا سال 2020 از سوکت فعلی AM4 پشتیبانی میکند، بنابراین محتمل به نظر میرسد در سال 2020 شاهد معرفی یک سوکت جدید با پشتیبانی از DDR5 باشیم.

هدف اصلی که با حافظه رم DDR5 دنبال میشود، افزایش پهنای باند، به ویژه برای سیستمهای مورد استفاده در محیطهای حرفهای و دیتا سنترها است. اگر بر روی کاغذ حافظه 3200 مگاهرتزی DDR4 را با DDR5 مقایسه کنیم، پهنای باند نسل جدید 1.36 برابر خواهد بود. با این حال از آنجایی که انتظار نمیرود نسل اول تراشههای DDR5 کُندتر از 4800MT/s باشند، افزایش پهنای باند میتواند 1.87 برابر باشد. استاندارد DDR5 بیشینه نرخ تبادل 6400MT/s را پیشبینی کرده اما ممکن است روزی شاهد عبور برخی سازندگان از آن باشیم.

40 عکس نقاشی دخترانه جدید، ساده، زیبا، فانتزی و آسان برای پروفایل

40 عکس نقاشی دخترانه جدید، ساده، زیبا، فانتزی و آسان برای پروفایل  دانلود آهنگ خاص و بی نظیر اجتماعی سارینا از شاهین نجفی

دانلود آهنگ خاص و بی نظیر اجتماعی سارینا از شاهین نجفی  40 گیف متحرک با طرح قلب برای واتساپ و تلگرام

40 گیف متحرک با طرح قلب برای واتساپ و تلگرام  صدای کوتوله برزیلی برای آموزش و سریع حرف زدن

صدای کوتوله برزیلی برای آموزش و سریع حرف زدن  لخته خون گوشتی شبیه جگر در پریودی چیست و چه علتی دارد؟ +روش درمان

لخته خون گوشتی شبیه جگر در پریودی چیست و چه علتی دارد؟ +روش درمان  هیچگاه موز و تخم مرغ را باهم نخورید

هیچگاه موز و تخم مرغ را باهم نخورید  انواع فونت و متن بسم الله الرحمن الرحیم برای بیو اینستا

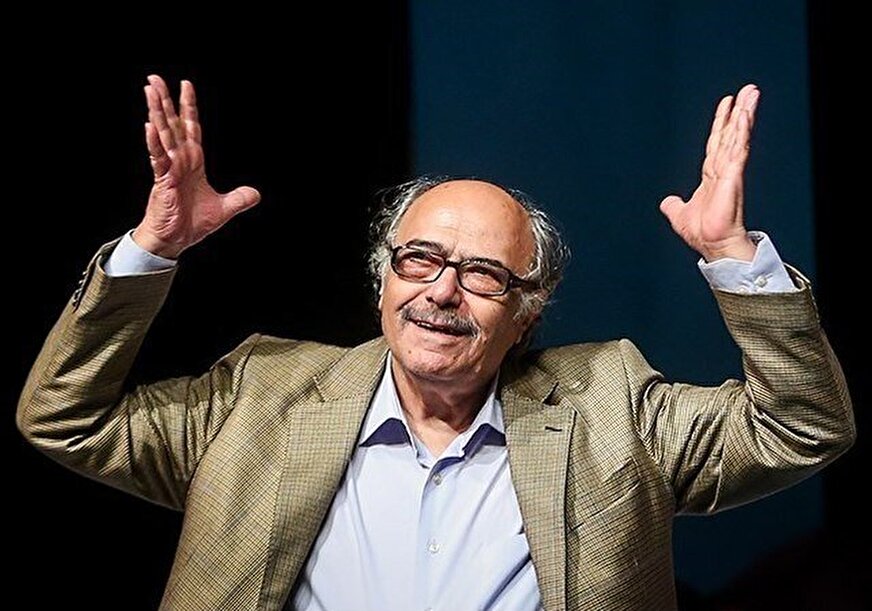

انواع فونت و متن بسم الله الرحمن الرحیم برای بیو اینستا  بزرگداشت اکبر زنجان پور و دو جای خالی

بزرگداشت اکبر زنجان پور و دو جای خالی  عکس | قابی دیدنی از بازیگر زن پُرحاشیه در حرم امام رضا(ع)

عکس | قابی دیدنی از بازیگر زن پُرحاشیه در حرم امام رضا(ع)  جملات و متن تبریک روز جهانی خلبان به همسرم و عشقم + عکس نوشته و استوری

جملات و متن تبریک روز جهانی خلبان به همسرم و عشقم + عکس نوشته و استوری  فال روزانه شنبه 8 اردیبهشت 1403

فال روزانه شنبه 8 اردیبهشت 1403  رابطه جنسی زیر دوش آب در حمام با همسر خوب است یا بد؟

رابطه جنسی زیر دوش آب در حمام با همسر خوب است یا بد؟  «اَللّهُمَّ عَجِّل لِوَلیِّکَ الفَرَج»، بهترین دعا و ظهور بزرگترین جایزه لیله الرغائب است

«اَللّهُمَّ عَجِّل لِوَلیِّکَ الفَرَج»، بهترین دعا و ظهور بزرگترین جایزه لیله الرغائب است  صفر تا صد عروسی های فریبا نادری + عکس مراسم های ازدواج خانم بازیگر !

صفر تا صد عروسی های فریبا نادری + عکس مراسم های ازدواج خانم بازیگر !  دانلود آهنگ ذوقم وه یه که بیای بشنوم دنگ صدات

دانلود آهنگ ذوقم وه یه که بیای بشنوم دنگ صدات